# VERIFIED CONFIGURATION OF PROGRAMMABLE NETWORKS

A Dissertation

Presented to the Faculty of the Graduate School of Cornell University

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

by Eric Hayden Campbell December 2024 © 2024 Eric Hayden Campbell ALL RIGHTS RESERVED

## VERIFIED CONFIGURATION OF PROGRAMMABLE NETWORKS

Eric Hayden Campbell, Ph.D.

Cornell University 2024

Reasoning about network programs is challenging because of how they divide labor: the control plane computes high level routes through the network and compiles them to device configurations, while the data plane uses these configurations to realize the desired forwarding behavior. In practice, the correctness of the data plane often assumes that the configurations generated by the control plane will satisfy complex specifications. These specifications are either missing or maintained in complex English language documents, which makes correctly configuring devices hard.

This thesis tackles this problem from three angles. First, we present algorithms for computing control plane interface specifications that ensure the safety of the data plane. These specifications can be used to improve the safety and quality of both the control plane and of the data plane. Then, we show how to automatically generate configurations for data plane programs, and finally, we conclude with a semantic framework for programming and relational verification of pairs of configurable programs.

#### **BIOGRAPHICAL SKETCH**

Eric Hayden Campbell was born at the University of Chicago hospital in 1995. Raised primarily in San Jose, California, he and his family moved to Amsterdam in 2011. He graduated from the International School of Amsterdam in 2013, at which point, he moved back to California to attend Pomona College. There he fell in love with computer science, discrete mathematics, and formal logic, receiving his bachelor's degrees in Mathematics and in Computer Science in 2017. For Priya, who never pulled punches

#### ACKNOWLEDGEMENTS

First and foremost, thanks to my advisor, Nate. Over the years, Nate has put up with my crackpot ideas and guided me through numerous eleventh-hour paper pushes. I thank him for his unwavering support and guidance.

I would also be remiss if I didn't thank Hossein Hojjat for being my formal methods guru: introducing me to synthesis and the formal methods community at large.

Thanks to Mark Moeller for moral support, running support, and for never being too good for a free banana. Thanks to Ryan Doenges for encouraging me, by example, to only do exactly what I wanted to do. Thanks to Jonathan DiLorenzo for mentoring me in health, wine, and cheese.

Thanks to Ryland Bednarek, Kiran Tomlinson, Mario Sanchez, Nora Murphy, Morgan Shelton, Peter Chwazik, and Marty Heresniak, for pushing my musical development, and giving me a creative restful outlet that has, through the years, supported my main academic endeavors.

And to Jane Lu, thanks for the endless dancing, singing, and outdoor adventures.

|   | Biographical Sketch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | iii<br>iv<br>v<br>vi<br>ix<br>x                                                    |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Ι | The Problem of Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                  |

| 1 | Managing Changing Programs         1.1       A Subprime Meridian         1.2       Improving P4 as a Specification Language         1.3       Leveraging Specifications         1.4       Summary of Contributions         1.5       Attribution and Acknowledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>2</b><br>3<br>4<br>6<br>8<br>10                                                 |

| 2 | Data Plane Programming       Image: State of the state o | <ol> <li>12</li> <li>18</li> <li>20</li> <li>21</li> <li>23</li> <li>25</li> </ol> |

| 3 | 3.1       A "Featherweight" P4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>26</b><br>29<br>32<br>35<br>40<br>43<br>45<br>46<br>48<br>53                    |

| 4 | 4.1       The Guarded Command Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>55</b><br>56<br>59<br>60<br>60<br>61<br>62                                      |

## TABLE OF CONTENTS

|          |          | 4.3.4  | Stateful Operations                                                                                                                                                             | 62         |

|----------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|          |          | 4.3.5  | Match-Action Tables                                                                                                                                                             | 62         |

|          | 4.4      | A Firs | st Attempt: Manual Control Interface Specs                                                                                                                                      | 63         |

| II       | C        | ontro  | ol Interface Specifications                                                                                                                                                     | 66         |

| <b>5</b> | Cor      |        | ng Precise Control Interface Specifications                                                                                                                                     | 67         |

|          | 5.1      | Backg  | ground and Motivation                                                                                                                                                           | 71         |

|          |          | 5.1.1  | Inference of Control Interface Specifications                                                                                                                                   |            |

|          |          | 5.1.2  | Previous Work                                                                                                                                                                   | 76         |

|          | 5.2      |        | ling                                                                                                                                                                            |            |

|          |          | 5.2.1  | Theories of Fixed-width Bitvectors                                                                                                                                              | 78         |

|          |          | 5.2.2  | Syntax and Semantics of the Guarded Pipeline Language                                                                                                                           |            |

|          |          |        | (GPL)                                                                                                                                                                           |            |

|          |          | 5.2.3  | Modeling Tables as Uninterpreted Functions                                                                                                                                      |            |

|          |          | 5.2.4  | Symbolic Compilation                                                                                                                                                            |            |

|          | 5.3      | Comp   | uting Efficiently Control-Monitorable Sentences                                                                                                                                 |            |

|          |          | 5.3.1  | QE Computes Precise ci-specs                                                                                                                                                    |            |

|          |          | 5.3.2  | Precise ci-spec Inference in ECMS Solves QE                                                                                                                                     | 95         |

|          | 5.4      | Progra | $\operatorname{ammatic} \operatorname{QE} \ldots \ldots$ |            |

|          |          | 5.4.1  | Paths Produce Smaller QE Problems                                                                                                                                               |            |

|          |          | 5.4.2  | A Path-Based Iterative Strengthening Algorithm                                                                                                                                  |            |

|          | 5.5      | -      | fications for Data Planes                                                                                                                                                       |            |

|          | 5.6      | -      | mentation $\ldots$                                                                             |            |

|          | 5.7      | Exper  | ience                                                                                                                                                                           | 104        |

|          |          | 5.7.1  | Capisce in Practice                                                                                                                                                             | 105        |

|          |          | 5.7.2  | True Data-Plane Bugs                                                                                                                                                            | 108        |

|          |          | 5.7.3  | Bugs Found by Inspecting ci-specs                                                                                                                                               | 110        |

|          |          | 5.7.4  | Analyzing Path Decomposition                                                                                                                                                    |            |

|          |          | 5.7.5  | Limitations                                                                                                                                                                     | 114        |

|          |          | 5.7.6  | Comparison to bf4                                                                                                                                                               | 116        |

| II       | I        | Verifi | ed Configuration                                                                                                                                                                | 119        |

| c        | <b>A</b> |        |                                                                                                                                                                                 | 100        |

| 6        |          |        | cally Configuring the Data Plane                                                                                                                                                | 120<br>125 |

|          | 6.1      |        | ground and Motivation                                                                                                                                                           |            |

|          | 6.2      |        | ol Plane Synthesis                                                                                                                                                              |            |

|          |          | 6.2.1  | Basic Definitions and Verification                                                                                                                                              |            |

|          |          | 6.2.2  | Synthesizing Candidates via Sketches                                                                                                                                            |            |

|          |          | 6.2.3  | Counterexample-Guided Search                                                                                                                                                    |            |

|          |          | 6.2.4  | Synthesis Algorithm                                                                                                                                                             | 137        |

vii

6.2.5

|    | 6.3    | A Scale | able Solution: Incremental Synthesis                                                                                                        | 140 |

|----|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    |        | 6.3.1   | Single Counterexample-Guided Search                                                                                                         | 140 |

|    |        | 6.3.2   | Incremental Synthesis Algorithm                                                                                                             | 143 |

|    |        | 6.3.3   | Formal Properties                                                                                                                           | 144 |

|    | 6.4    | Heurist | tics and Optimizations                                                                                                                      | 145 |

|    |        | 6.4.1   | Exploiting Incrementality                                                                                                                   | 145 |

|    |        | 6.4.2   | Model-Finding Heuristics                                                                                                                    | 147 |

|    | 6.5    | Implen  | nentation                                                                                                                                   | 148 |

|    | 6.6    | Evalua  | $tion \ldots \ldots$ | 149 |

|    |        | 6.6.1   | Retargeting Study                                                                                                                           | 151 |

|    |        | 6.6.2   | Network Emulation                                                                                                                           | 153 |

|    |        | 6.6.3   | Case Study: Trellis & ONOS                                                                                                                  | 153 |

|    |        | 6.6.4   | Microbenchmarks                                                                                                                             | 155 |

|    | 6.7    | Limita  | tions and Future Work                                                                                                                       | 156 |

|    | 6.8    | Conclu  | $sion \ldots $                     | 157 |

|    |        |         |                                                                                                                                             |     |

| 7  |        |         |                                                                                                                                             | .59 |

|    | 7.1    |         |                                                                                                                                             | 162 |

|    | 7.2    |         | Definitions for Relational Hoare Lenses                                                                                                     |     |

|    |        | 7.2.1   | Specifications for lenses                                                                                                                   |     |

|    |        | 7.2.2   | Relational Hoare Lenses                                                                                                                     |     |

|    | 7.3    |         | onal Program Logics                                                                                                                         |     |

|    |        | 7.3.1   | Relational Hoare Logic                                                                                                                      |     |

|    |        | 7.3.2   | Reasoning about Programs with RHLenses                                                                                                      |     |

|    | 7.4    | -       | nentation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$                                                                                  |     |

|    | 7.5    |         | tudy: Network Data Plane Programs                                                                                                           |     |

|    |        | 7.5.1   | Source Program                                                                                                                              |     |

|    |        | 7.5.2   | Action Decompose                                                                                                                            |     |

|    |        | 7.5.3   | Metadata Decomposition                                                                                                                      |     |

|    |        | 7.5.4   | Early Validation                                                                                                                            | 195 |

| 8  | Rela   | ated W  | <sup>7</sup> ork 1                                                                                                                          | .97 |

|    |        |         |                                                                                                                                             |     |

| 9  | Con    | clusion |                                                                                                                                             | 202 |

|    | 9.1    | Future  | Work                                                                                                                                        | 204 |

| Bi | ibliog | graphy  | 2                                                                                                                                           | 206 |

## LIST OF TABLES

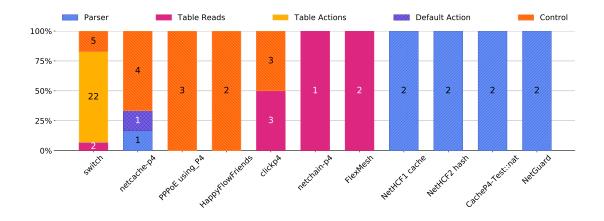

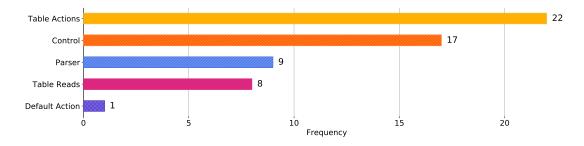

| 5.1 | Experience with using Capisce to check Header Validity on a broad |     |

|-----|-------------------------------------------------------------------|-----|

|     | range of P4 programs.                                             | 106 |

| 5.2 | Experience with using Capisce to check Determined Forwarding on   |     |

|     | a broad range of P4 programs.                                     | 107 |

## LIST OF FIGURES

| Abstract forwarding model                                            | 13                                                                                                                                                                   |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                      |                                                                                                                                                                      |

| header optionally followed by VLAN and/or IPv4 headers. (Right)      |                                                                                                                                                                      |

| P4 code implementing the same parser.                                | 14                                                                                                                                                                   |

| P4 tables. forward reads the validity of the ipv4 and vlan header    |                                                                                                                                                                      |

| · –                                                                  |                                                                                                                                                                      |

| -                                                                    | 15                                                                                                                                                                   |

|                                                                      | 17                                                                                                                                                                   |

|                                                                      |                                                                                                                                                                      |

|                                                                      | 19                                                                                                                                                                   |

|                                                                      | 10                                                                                                                                                                   |

|                                                                      | 20                                                                                                                                                                   |

|                                                                      | 20                                                                                                                                                                   |

|                                                                      | 22                                                                                                                                                                   |

| 0 01                                                                 | $\frac{22}{24}$                                                                                                                                                      |

|                                                                      | $\frac{24}{25}$                                                                                                                                                      |

| Left. unsale code in NETCACHE, fugit. our type-sale fix              | 20                                                                                                                                                                   |

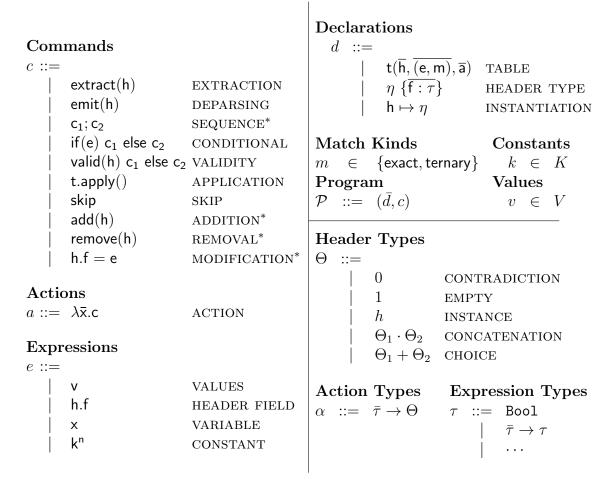

| Syntax of SafeP4                                                     | 33                                                                                                                                                                   |

|                                                                      | 36                                                                                                                                                                   |

|                                                                      | 37                                                                                                                                                                   |

|                                                                      | 39                                                                                                                                                                   |

|                                                                      | 39                                                                                                                                                                   |

|                                                                      | 00                                                                                                                                                                   |

|                                                                      | 41                                                                                                                                                                   |

|                                                                      | 42                                                                                                                                                                   |

|                                                                      | 44                                                                                                                                                                   |

|                                                                      | 43                                                                                                                                                                   |

| 01                                                                   | 40                                                                                                                                                                   |

|                                                                      |                                                                                                                                                                      |

|                                                                      | 46                                                                                                                                                                   |

| 1                                                                    | 40                                                                                                                                                                   |

|                                                                      | 46                                                                                                                                                                   |

|                                                                      | 40                                                                                                                                                                   |

|                                                                      | 40                                                                                                                                                                   |

| · · · · · · · · · · · · · · · · · · ·                                | 49                                                                                                                                                                   |

|                                                                      | 50                                                                                                                                                                   |

| actions bug (bottom)                                                 | 50                                                                                                                                                                   |

| Syntax (left) and somentics (right) of the Guarded Command Lan       |                                                                                                                                                                      |

|                                                                      | 56                                                                                                                                                                   |

|                                                                      | 58                                                                                                                                                                   |

| Divector Artumiente, expressions (lett) and logical formulae (light) | 00                                                                                                                                                                   |

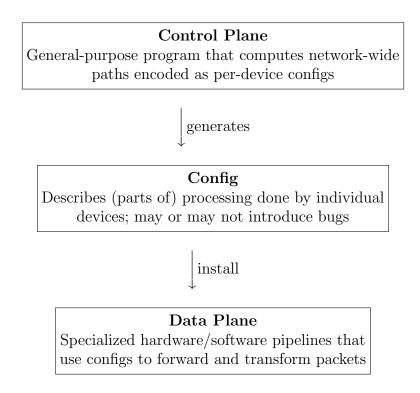

| The control plane generates configs that define data plane behavior. | 67                                                                                                                                                                   |

|                                                                      | (Left) Header formats and parse graph that extracts an Ethernet header optionally followed by VLAN and/or IPv4 headers. (Right) P4 code implementing the same parser |

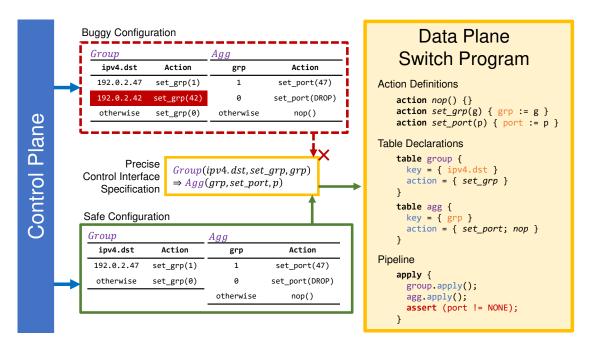

| <ul> <li>configs, like the one shown on the bottom, are accepted and can be safely installed into the pipeline program</li></ul>                                                                                                                                                                                                                                                                                                                                                            |       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| <ul> <li>right), depending on whether they allow quantifiers (∀) and/or un-<br/>interpreted functions (F). The semantics of bitvector expressions<br/>are standard.</li> <li>5.4 Syntax (left) and semantics (right) of Guarded Pipeline Language<br/>GPL(T) over a bitvector theory T. Highlighted variants only occur<br/>in GPL(T); the other variants are Guarded Command Language<br/>GCL(T).</li> <li>5.5 Path coverage over time for Header Validity analysis of programs</li> </ul> | . 72  |

| <ul> <li>5.4 Syntax (left) and semantics (right) of Guarded Pipeline Language GPL(T) over a bitvector theory T. Highlighted variants only occur in GPL(T); the other variants are Guarded Command Language GCL(T).</li> <li>5.5 Path coverage over time for Header Validity analysis of programs</li> </ul>                                                                                                                                                                                 |       |

| <ul> <li>GPL(T) over a bitvector theory T. Highlighted variants only occur in GPL(T); the other variants are Guarded Command Language GCL(T).</li> <li>5.5 Path coverage over time for Header Validity analysis of programs</li> </ul>                                                                                                                                                                                                                                                      | . 78  |

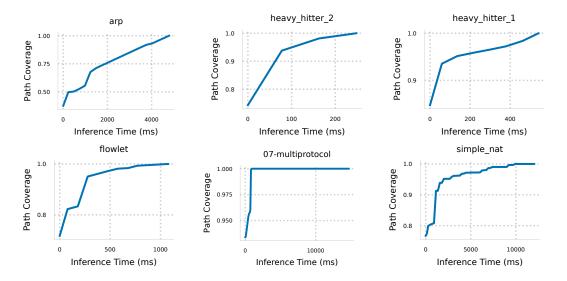

| 5.5 Path coverage over time for Header Validity analysis of programs                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 80  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 112 |

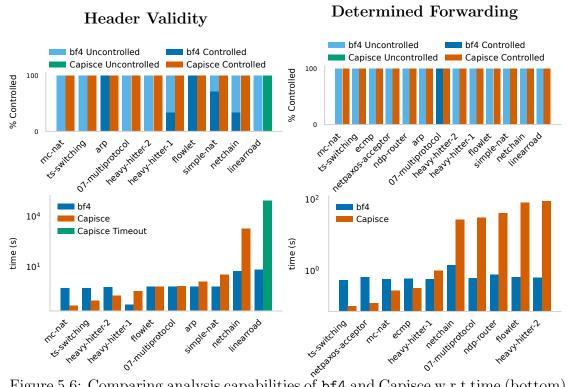

| 5.6 Comparing analysis capabilities of bf4 and Capisce w.r.t time (bot-                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| tom) and bugs controlled (top). Note the logarithmic $y$ -axes on the                                                                                                                                                                                                                                                                                                                                                                                                                       | 117   |

| time charts. $\ldots$                                                                                                                                                                                                                                                                                                                                                                                      | . 117 |

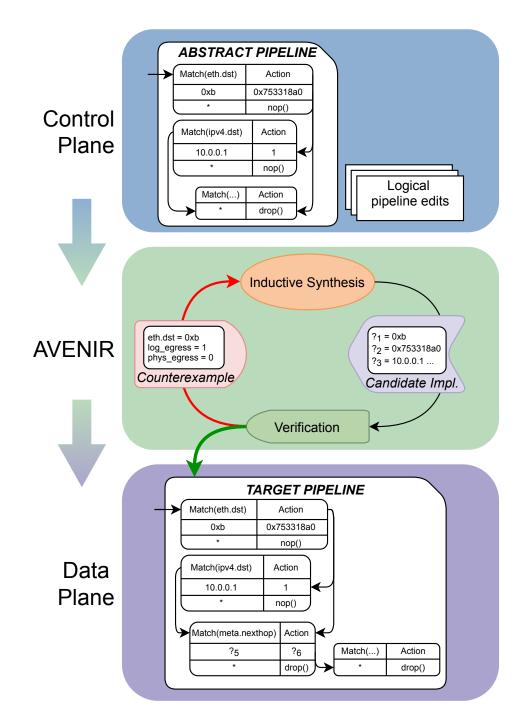

| 6.1 Avenir maps control plane operations for an abstract pipeline into corresponding operations for a target using sketch-based synthesis. The synthesis loop alternates between verifying the correctness of a candidate implementation and learning from counterexamples to generate a better one; the holes (e.g., ? <sub>5</sub> ) in the target sketch denote                                                                                                                          |       |

| missing values that are filled in using an SMT solver.                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 124 |

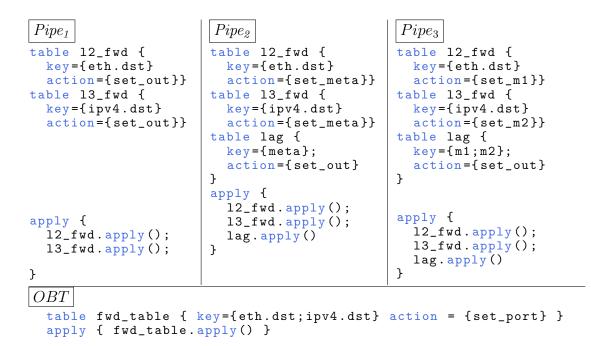

| 6.2 Pipelines used in example scenario                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| 6.3 The Status Quo Manual translations from Pipeline 1 to Pipelines                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| 2 and 3. Avenir automates theses translations entirely $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                    | . 125 |

| 6.4 <b>The Status Quo</b> : Manual translations in pseudocode from "one                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| big table" $(OBT)$ to Pipelines 1 through 3                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 126 |

| 6.5 Dynamic Configurations used in example scenario. $Pipe_2$ is an-                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| notated with "holes" to be filled in. During synthesis, Avenir                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| solves for these unknowns and concludes that $?_1 = ABB28FC$ ,                                                                                                                                                                                                                                                                                                                                                                                                                              | 100   |

| $?_2 = \text{set}_{\text{meta}}(5), ?_3 = 5, ?_4 = \text{set}_{\text{out}}(5), \dots \dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                     |       |

| 6.6 Pipeline syntax. Actions vary under starred variants                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

| 6.7 Summary of holes used in sketching                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 139 |

| 6.8 The model function. In the above, the vector $\overline{x}$ is all of the non-hole variables that occur in the formula.                                                                                                                                                                                                                                                                                                                                                                 | . 137 |

| 6.9 Simple Algorithm for Control Plane Synthesis.                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| $6.10$ Basic Sketch for $Pipe_1$ : Satisfiable for packets that hit L2's first                                                                                                                                                                                                                                                                                                                                                                                                              | 101   |

| row and L3's second                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 138 |

| 6.11 | Incremental Sketch for $Pipe_1$ : Unsatisfiable for packets that hit L2's                               |

|------|---------------------------------------------------------------------------------------------------------|

|      | first row and L3's second, which triggers backtracking, remember-                                       |

| 6.12 | ing that the previously-synthesized edit was incorrect                                                  |

| 0.12 | comodate the counterexample $\chi$ . The oracle soundly restricts the                                   |

|      | search space. $\ldots$ |

| 6.13 | The incremental backtracking CEGIS algorithm                                                            |

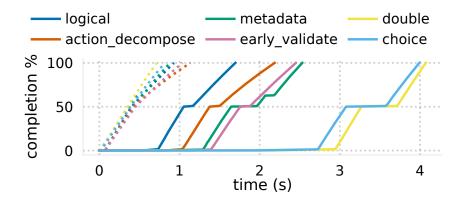

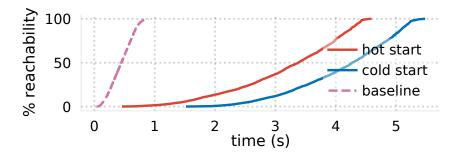

| 6.14 | Retargeting case study: solid lines show cold-start completion %;                                       |

| 0.11 | dotted lines show hot-start completion %                                                                |

| 6.15 | Proportion of all pairs of 64 hosts connected in a star topology that                                   |

|      | have completed a successful IPv4 ping                                                                   |

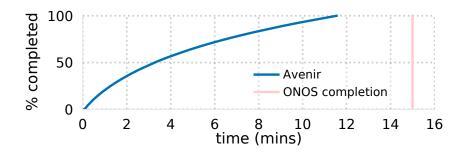

| 6.16 | Completion graph for mapping 40k fabric.p4 IPv6 route insertions                                        |

|      | onto bcm.p4; ONOS takes around 15 min                                                                   |

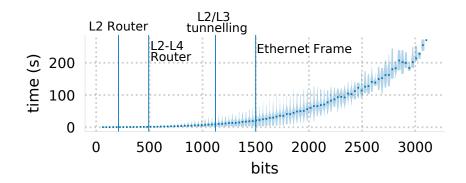

| 6.17 | Program bits vs time to translate 100 edits. The vertical lines                                         |

|      | estimate the sizes of common router programs                                                            |

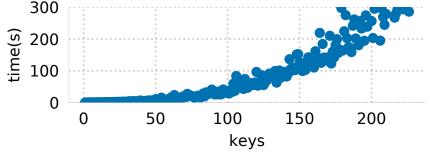

| 6.18 | Classifier Scaling. We fixed the number of 32-bit output variables                                      |

|      | to 8, and varied the number of keys                                                                     |

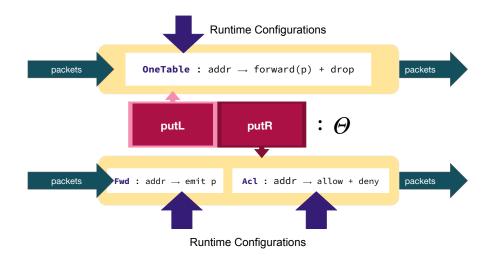

| 7.1  | A lens synchronizing abstract and concrete views of a packet for-                                       |

|      | warding pipeline. The relation $\Theta$ describes the relation maintained                               |

|      | by the lens's $putR$ and $putL$ functions                                                               |

| 7.2  | A judgment defining whether a configuration is valid $w.r.t.$ a schema 173                              |

| 7.3  | Syntax (left), denotational semantics (right) , and auxiliary sets                                      |

|      | (bottom) for WHILE                                                                                      |

| 7.4  | The syntax (left) and semantics of relational expressions (middle)                                      |

|      | and formulae (right)                                                                                    |

| 7.5  | Structural axioms and inference rules for closed programs [15, 9] 179                                   |

| 7.6  | Correpondence between the RHL proof system and RHLens com-                                              |

| 7.7  | binators                                                                                                |

| 1.1  | 0 1 1                                                                                                   |

| 7.8  | Modules describing Lenses (right) and the configurations they act                                       |

| 1.0  | upon (left)                                                                                             |

|      |                                                                                                         |

# Part I

# The Problem of Interfaces

#### CHAPTER 1

#### MANAGING CHANGING PROGRAMS

The Internet was built on standards. Standardization bodies produce specification documents that describe numerous standardized protocols for enabling communication between devices. These protocols specify intricate message formats, semantics, and patterns. Having a robust set of protocols with agreed-upon semantics enables decentralized growth of computer networks. That is, an engineer who faithfully implements a standardized communication protocol, such as BGP, can generally believe that their implementation will be able to communicate with any other BGP-enabled device.

Modern networking architectures promote a different set of values. From the reliable model of rigid standardization, design patterns like software-defined networking (SDN) and deep network programability [52] permit flexibility and agility in network design. For instance, the programming language P4 allows engineers to *program protocol-independent packet processors* [20]. That is, engineers are able to define their own packet-level communication formats and forwarding patterns to suit their specific needs.

However, this preponderance of data formats is dangerous for system reliability. As any standardization committee will tell you, the path to "rough consensus and working code" is a long one, requiring many iterations before the protocol is standardized. Indeed, the modern Internet protocol suite is the result of decades of debate and scores of revisions. Similarly, bespoke packet processing logic typically requires many iterations before it reaches a stable state. As we'll see, each of these changes to the packet processing logic can have significant ramifications throughout the networking software stack. Rather than yearn for the good old days of standardization, this dissertation proposes formal tools that help us move *with* the constant ebb and flow of software development for packet processors. If we can formally understand the ramifications of various changes (Chapter 5), abstract changes away entirely (Chapter 6), and/or reason about changes formally (Chapter 7), we can more robustly manage the variation and evolution of packet processing software.

## 1.1 A Subprime Meridian

The computer network is divided by an architectural meridian: the interface between the control plane and the data plane. The control plane does the complex computational work: computing routes through the network to ensure requests get served, deciding which potentially malicious agents to block to ensure they cannot access sensitive data, or balancing the network load between hosts to ensure that no one gets overwhelmed. Meanwhile, the data plane—which is a collection of hardware that is highly-specialized to rapidly and efficiently transform and transfer internet data packets—realizes the control plane's policies. We use the term *switch* to refer to an abstract data plane forwarding device. To enact high-level policies, the control plane configures the data plane's behavior using the *control plane interface*.

Unfortunately, the control plane interface is poorly specified. Traditionally, hardware vendors release switches alongside lengthy English language documents that describe the control plane interface. However, these specifications are often insufficient, leaving significant behaviors undefined, underspecified, or simply incorrect.

Network engineers have been using P4 to shore up the robustness of the control-

plane interface. Optimistically, network engineers write P4 code that is compiled directly to a configurable hardware format. The P4 code specifies both structure of the interface, and the forwarding logic that relies on that interface. Conceptually, the P4 code implements the *semantics* of the interface. However, after Intel's recent cancelation of its flagship P4-enabled switch line, Tofino, using P4 to implement real computer networks is less common.

A more widely applicable use case of P4, is as a *specification* language. Network engineers, especially at Google, have been using P4 to specify fixed-function, i.e. non-programmable, switches from vendors like Broadcomm [2]. These specification programs can be used bi-directionally, both to characterize correct behavior for the data plane switch it models and to characterize correct behavior for the control plane. This has enabled engineers to perform automatic verification [72, 108] and to generate concrete packets and configurations to use as test cases for the data plane [97].

## 1.2 Improving P4 as a Specification Language

Unfortunately, P4 was designed for *programming*, not *specification*, which has caused some growing pains. A very sensible language design decision—especially for a language that is meant to be amenable to many different hardware targets—is to allow compiler designers significant freedom in interpreting the language. In the specification, this is characterized as *undefined behavior*. Largely, the P4 language limits undefined behavior, but there are a few places it can arise.

Undefined behavior presents a challenge to using P4 as a specification language, because its presence is generally not apparent to the programmer. In Section 2.1 we discuss a collection of bugs in real P4 programs where possibly-uninitialized data was accessed—in P4, reading uninitialized data returns an undefined value.

In Chapter 3 we define a type system for an "featherweight" version of P4 called SafeP4 that avoids reading unintialized data. We use an occurence-style type system, and prove that our analysis is sound and complete. We also analyze a collection of P4 programs and propose a taxonomy of of code repairs that corresponds to the taxonomy of bugs from Section 2.1.

We can generalize these observations beyond just avoiding undefined behavior. In general, a P4 program may have its own *correctness specification* that must be satisfied: e.g. IPv4 and IPv6 can never exist simultaneously in a single packet, or an emitted packet's time-to-live (TTL) field is never zero (which should indicate that the packet should be dropped, and an error packet returned to the sender).

Ideally, P4 programs-as-specifications would be written to satisfy the data plane correctness specification for every possible way that the control plane could configure it. However, in practice, programmers often make assumptions about the content of the configurations (i.e. that they must adhere to complex invariants). As a result, verification tools require assumptions about the behavior of the control plane. For instance, SafeP4 (Chapter 3) makes a collection of assumptions that the control plane is locally-sensible. That is, we assume that the control plane never reads invalid data. However, if even in the presence of these assumptions, the controller can configure the tables in a way that allows invalid data to be read, the program will be rejected by the type system.

Taking a step back, we want a general framework for characterizing limitations on the control plane. Existing work on p4-constraints, and p4v (see Chapter 4) has proposed using of first-order formulae to constrain the control plane interface. These *control plane interface specs* (ci-specs) are very useful; they can be used to: runtime-monitor the control plane, fuzz-test the control plane and the data plane, or even use them in a formal verification context. However, network engineers are not used to writing specifications.

In Chapter 5 we propose Capisce, a framework for inferring ci-specs automatically—taking as input a switch program and its correctness specification. The ci-specs  $\psi$  computed by Capisce are *precise*: a configuration satisfies  $\psi$  if and only if there are no reachable bugs in the switch program. They are also *efficiently control-monitorable*, which means that for a fixed configuration, evaluating  $\psi$  is polynomial.

Having precise ci-specs closes the loop on using P4 as a programming-andspecification language for switches. Now programmers have an executable P4 program that gives precise semantics to the interface, and a set of constraints the ci-spec—that describes the correct use of the program.

## **1.3** Leveraging Specifications

We'll see that once we can precisely characterize the control plane interface, we can manage the variability and diversity that is inherent to computer networks. Most network operators build networks to support a varied collection of hardware, which results in devices with heterogeneous feature sets. This heterogeneity manifests as complexity throughout the control plane.

To manage device heterogeneity, network engineers can leverage abstraction—

designing a unifying logical interface to support the motley collection of physical switches. Of course, both the unifying logical interface and the corresponding switches and can be specified as P4 programs. For example, in the Open Network Operating System (ONOS [17]), the high-level interface is specified using a P4 program called fabric.p4, which is then mapped down to an array of target devices, which are either implemented or specified in P4.

The handwritten mapping code that synchronizes the configurations of logical and target programs is expensive to develop and error prone to build and maintain. To make matters worse, and every incremental change to a switch program or minor difference between switches can result in wide-sweeping changes. ONOS engineers shared an example (more in Chapter 6) of a seemingly trivial data plane change that broke abstraction boundaries and propagated all the way to the network application logic.

In Part III we leverage code as specifications to synchronize the interface of the logical and target programs in a verified manner. Concretely, we want to ensure with synchronized configs, the logical and target programs are equivalent.

In Chapter 6 we present Avenir, an automated synthesis tool that translates configs in an equivalence-preserving way. Importantly, our algorithm is incremental, which allows it to be fast and avoid significant recomputation work when the configurations get sizable. Alongside formal proofs of correctness, our evaluation on handcrafted benchmarks, industrial programs, and microbenchmarks shows that Avenir is scalable and expressive.

However, as with any synthesis tool, there will be times when Avenir cannot find a solution in a reasonable amount of time—even when one exists. So some degree of manual intervention is desirable. Further, Avenir's synchronization only works in one direction, and there are on-switch gadgets that can modify the configurations unbeknownst to the control plane.

The final chapter, Chapter 7 provides a semantic framework for reasoning about synchronizing pairs of reconfigurable programs. Synthesizing decades of work in bidrectional programming [50] and relational hoare logic [16], we propose *relational hoare lenses* (RHLenses), which allow us to reason about relational program properties, like equivalence, in the presence of synchronization code—the *lenses*. Indeed, relational hoare lenses has more general applications than just synchronizing network dataplanes, including in security, databases, and operating systems, but for this thesis we focus on this networking application, showing that we can use RHLenses to model the handcrafted benchmarks we used to evaluate Avenir.

## **1.4 Summary of Contributions**

We summarize the contributions of this thesis as follows:

• Chapter 3 describes SafeP4, a domain-specific language for programmable data planes in which all packet data is guaranteed to have a well-defined meaning and satisfy essential safety guarantees. SafeP4 is equipped with a formal semantics and a static type system that statically guarantees header validity—a common source of safety bugs, according to our analysis of real-world P4 programs. Statically ensuring header validity is challenging because the set of valid headers can be modified at runtime, making it a dynamic program property. Our type system achieves static safety by using a form of path-sensitive reasoning that tracks dynamic information from conditional

statements, routing tables, and the control plane. Our evaluation shows that SafeP4's type system can effectively eliminate common failures in many real-world programs.

- Chapter 5 describes the first algorithm for computing precise ci-specs for network data planes. Our specifications are designed to be efficiently monitorable—concretely, checking that a fixed configuration satisfies a ci-spec can be done in polynomial time. Our algorithm, based on modular program instrumentation, quantifier elimination, and a path-based analysis, is more expressive than prior work, and is applicable to practical network programs. We describe an implementation and show that ci-specs computed by our tool are useful for finding real bugs in real-world data plane programs.

- Chapter 6 describes Avenir, a synthesis tool that automatically generates control-plane operations to ensure uniform behavior across a variety of data planes. Our approach uses counter-example guided inductive synthesis and sketching, adding network-specific optimizations that exploit domain insights to accelerate the search. We prove that Avenir's synthesis algorithm generates correct solutions and always finds a solution, if one exists. We have built a prototype implementation of Avenir using OCaml and Z3 and evaluated its performance on realistic scenarios for the ONOS SDN controller and on a collection of benchmarks that illustrate the cost of retargeting a control plane from one pipeline to another. Our evaluation demonstrates that Avenir can manage data plane heterogeneity with modest overheads

- Chapter 7 proposes a new framework for synchronizing configurable programs, called Relational Hoare Lenses (RHLenses). As the name suggests, this framework can be seen as the marriage of two apparently unrelated lines of work: one focused on the design of bidirectional programming constructs

and the other focused on logical tools for reasoning about pairs of programs. The combination of these two approaches is both elegant and powerful. As we will show in this paper, RHLenses neatly generalize prior work on relational program logics, and we believe they can be used to solve practical problems as well.

### **1.5** Attribution and Acknowledgements

The work presented in this these comprises work from a collection of papers:

- Chapter 2 and Chapter 3 are based on the following publication, which also appeared in Eichholtz's dissertation Eichholz, Matthias, Eric Hayden Campbell, Nate Foster, Guido Salvaneschi and Mira Mezini. 2019. How to Avoid Making a Billion-Dollar Mistake: Type-Safe Data Plane Programming with SafeP4. 33rd European Conference on Object-Oriented Programming, ECOOP, (July 2019)

- Chapter 4 and Chapter 5 are based on the following publication: Eric Hayden Campbell, Hossein Hojjat, and Nate Foster. 2024. Computing Precise Control Interface Specifica- tions. Proceedings of the ACM on Programming Languages 8, OOPSLA2(October 2024).

- 3. Chapter 6 is based on the following publication: Eric Hayden Campbell, William T. Hallahan, Carmelo Cascone, Jed Liu, Vignesh Ramamurthy, Hossein Hojjat, Ruzica Piskac, Robert Soule, and Nate Foster. 2021. 18th USENIX Symposium on Networked Systems Design and Implementation, NSDI (April 2021)

4. Chapter 7 is based on in-review work with the following attribution: Eric Hayden Campbell, Mark Barbone, and Nate Foster. 2024. In Review.

## CHAPTER 2 DATA PLANE PROGRAMMING

Luck is a very thin wire between survival and disaster, and not many people can keep their balance on it.

Hunter S. Thompson

Before we can get into verified configuration, we need to develop a working model of data plane programming. As our guide, we'll use the *de facto* industry standard data plane programming language called P4. Rather than model P4's full complexity, we'll focus primarily on the core constructs of the language related to its interface with the control plane.

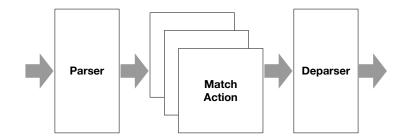

P4 is a domain-specific language designed for processing packets—i.e., arbitrary sequences of bits that can be divided into (i) a set of pre-determined *headers* that determine how the packet will be forwarded through the network, and (ii) a *payload* that encodes application-level data. P4 is designed to be protocol-independent, which means it handles both packets with standard header formats (e.g., Ethernet, IP, TCP, etc.) as well as packets with custom header formats defined by the programmer. Accordingly, a P4 program first *parses* the headers in the input packet into a typed representation. Next, it uses a *match-action pipeline* to compute a transformation on those headers—e.g., modifying fields, adding headers, or removing them. Finally, a *deparser* serializes the headers back into a packet, which can be output to the next device. A depiction of this abstract forwarding model is shown in Figure 2.1.

Figure 2.1: Abstract forwarding model.

The match-action pipeline relies on a data structure called a *match-action table*, which encodes conditional processing. More specifically, the table first looks up the values being tested against a list of possible entries, and then executes a further snippet of code depending on which entry (if any) matched. However, unlike standard conditionals, the entries in a match-action table are not known at compile-time. Rather, they are inserted and removed at run-time by the control plane, which may be logically centralized (as in a software-defined network), or it may operate as a distributed protocol (as in a conventional network).

The rest of this section describes P4's typed representation, how the parsers, and deparsers convert between packets and this typed representation, and how control flows through the match-action pipeline.

**Header Types and Instances** Header types specify the internal representation of packet data within a P4 program. For example, the first few lines of the following snippet of code:

```

header ethernet_t {

dstAddr: bit<48>;

srcAddr: bit<48>;

etherType: bit<16>;

}

struct headers {

ethernet_t ethernet;

ethernet_t inner_ethernet;

}

```

declare a type (ethernet\_t) for the Ethernet header with fields dstAddr, srcAddr,

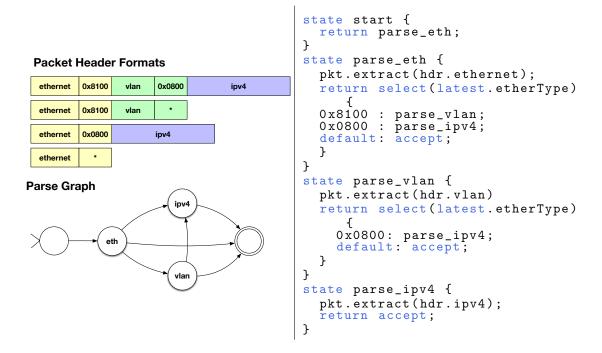

Figure 2.2: (Left) Header formats and parse graph that extracts an Ethernet header optionally followed by VLAN and/or IPv4 headers. (Right) P4 code implementing the same parser.

and etherType. The type of each field is provided after the colon. While P4 has a wide variety of types from strings, structs, to integers, we'll focus on fixedwidth bitvectors, which are the core of the packet-processing logic. Here bit < n >is the type of a bitvector comprising *n* bits. The struct called header declares two ethernet\_t instances (ethernet and inner\_ethernet) with global scope. Note that ordinary packets usually have a single Ethernet header, but a tunneling protocol might maintain a second header for encapsulated packets.

Further, each header is equipped with a validity bit that can be read via the method isValid(), assigned to true with setValid() and setInvalid(). The P4 language specification says that when a header h is invalid, the value returned by reading any any field in that header, e.g. h.f, is undefined.

```

table forward {

key = {

ipv4.isValid() : exact

;

ipv4.isValid() : exact

;

ipv4.dstAddr: ternary;

}

actions = {

nop;

next_hop;

remove;

}

default_action : nop();

}

```

Runtime Contents of forward

| Pattern |      |              | Action   |      |

|---------|------|--------------|----------|------|